## **Advanced Digital Design with the Verilog HDL**

M. D. Ciletti

Department of Electrical and Computer Engineering University of Colorado Colorado Springs, Colorado

#### ciletti@vlsic.uccs.edu

#### **Draft: Chap 6b: Synthesis of Combinational and Sequential Logic**

Copyright 2001, 2003. These notes are solely for classroom use by the instructor. No part of these notes may be copied, reproduced, or distributed to a third party, including students, in any form without the written permission of the author. (Rev 9/17/2003)

Note to the instructor: These slides are provided <u>solely for classroom use</u> in academic institutions by the instructor using the text, *Advance Digital Design with the Verilog HDL* by Michael Ciletti, published by Prentice Hall. This material may not be used in off-campus instruction, resold, reproduced or generally distributed in the original or modified format for any purpose without the permission of the <u>Author</u>. This material may <u>not</u> be placed on any server or network, and is protected under all copyright laws, as they currently exist. I am providing these slides to you subject to your agreeing that you will not provide them to your students in hardcopy or electronic format or use them for off-campus instruction of any kind. <u>Please email to me your agreement to these conditions</u>.

I will greatly appreciate your assisting me by calling to my attention any errors or any other revisions that would enhance the utility of these slides for classroom use.

## COURSE OVERVIEW

- Review of combinational and sequential logic design

- Modeling and verification with hardware description languages

- Introduction to synthesis with HDLs

- Programmable logic devices

- State machines, datapath controllers, RISC CPU

- Architectures and algorithms for computation and signal processing

- Synchronization across clock domains

- Timing analysis

Fault simulation and testing, JTAG, BIST

### Synthesis of Sequential Logic with Flip-Flops

Note: Flip-flops are synthesized only from edge-sensitive cyclic behaviors Questions:

- What determines the outcome of synthesis from an edge-sensitive behavior?

- How does a synthesis tool infer the need for a flip-flop?

- When does a register variable that is assigned value within an edgesensitive behavior automatically synthesize to a flip-flop?

- How does the synthesis tool distinguish the synchronizing signal (clock) from other signals in the event control expression of a cyclic behavior?

- How can multiple flip-flops or registers be modeled to operate concurrently?

#### **Inference of Flip-Flops**

Each of the following conditions imply the need for memory and will synthesize a register variable to a flip flop:

- The variable is referenced outside of the behavior

- The variable is referenced within the behavior before it is assigned value

- The variable is assigned value in only some of the branches of activity within the behavior

### Flip-Flops or Latches?

- Memory inferred for an edge-sensitive cyclic behavior will be synthesized as a flip flop

- Memory inferred for a level-sensitive cyclic behavior or a continuous assignment with feedback will be synthesized as a latch

- Note: an incomplete conditional statement (*if...else*) or a *case* statement in a level-sensitive cyclic behavior will synthesize to a latch.

- Note: an incomplete conditional statement statement (*if...else*) or a *case* statement in an edge-sensitive cyclic behavior will synthesize to a flip-flop with circuitry effectively implementing clock enable.

## Synchronizing Signal (1 of 2)

- The order in which signals appear in the event control expression of an edge-sensitive cyclic behavior does not determine which signal is the synchronizing signal

- The sequence in which signals are decoded in the statement that follows the event control expression of an edge-sensitive cyclic behavior determines which of the edge-sensitive signals are control signals and which is the clock (i.e., the synchronizing signal).

## Synchronizing Signal (2 of 2)

Note: If the event control expression is sensitive to the edge of more than one signal, an *if* statement must be the first statement in the behavior.

- The control signals that appear in the event control expression must be decoded explicitly in the branches of the *if* statement (e.g., decode the reset condition first).

- The synchronizing signal is not tested explicitly in the body of the if statement, but, by default, the last branch must describe the synchronous activity, independently of the actual names given to the signals.

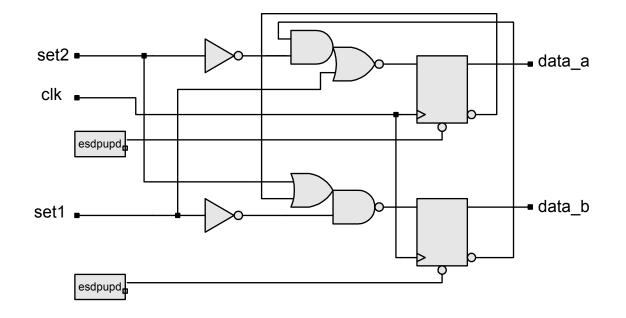

## Synthesis of a flip-flop

SYNTHESIS TIP

A variable that is referenced within an edge-sensitive behavior before it is assigned value by the behavior will be synthesized as the output of a flip-flop.

```

Example 6.23

module swap_synch (data_a, data_b, set1, set2, clk); // Typo at text

data_a, data_b;

// Typo at text

output

input clk, set1, set2;

data_a, data_b;

reg

always @ (posedge clk)

begin

if (set1) begin data_a <= 1; data_b <= 0; end else</pre>

if (set2) begin data_a <= 0; data_b <= 1; end else</pre>

else

begin

data b <= data a;

data a <= data b;

end

end

endmodule

```

- The statements assigning value to data\_a and data\_b execute non-blocking assignments concurrently

- Both variables are sampled (referenced) before receiving value

- Both are synthesized as the output of a flip-flop

- Notice that *set1* and *set2* are explicitly decoded first. The last clause of the *if* statement assigns values to *data\_a* and *data\_b*. Those (non-blocking) assignments are synchronized to the rising edge of *clk*, which is not referenced explicitly in the *if* statement.

## Synthesis result:

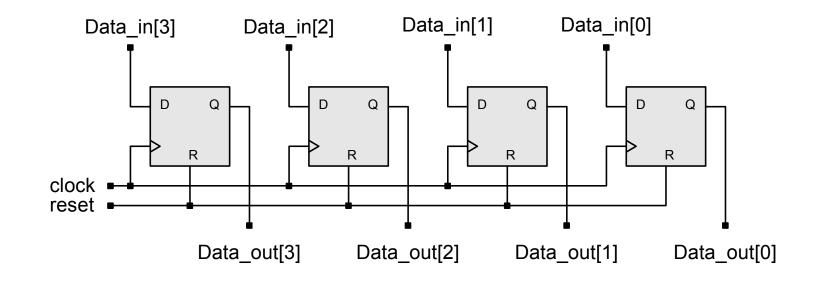

Example: Synthesis of a 4-bit Parallel Load Data Register

#### Example 6.24

```

module D_reg4_a (Data_out, clock, reset, Data_in);

output [3: 0] Data_out;

input [3: 0] Data_in;

input clock, reset;

reg [3: 0] Data_out;

always @ (posedge clock or posedge reset)

begin

if (reset == 1'b1) Data_out <= 4'b0;

else Data_out <= Data_in;

end

endmodule</pre>

```

Note:

- The positive edge of *reset* appears in the event control expression and appears in the first clause of the *if* statement

- The positive edge of *clock* also appears in the event control expression, but is not explicitly decoded by the branch statement that follows the event control expression.

Synthesis Result:

## Rules for Synchronizing Signals

- Synchronize an edge-sensitive cyclic behavior to a single edge (*posedge* or *negedge*, but not both) of a single clock (synchronizing signal)

- Multiple behaviors need not have the same synchronizing signal, or be synchronized by the same edge of the same signal

- All of the synchronizing signals (clocks) must have the same period

A variable that is assigned value by a cyclic behavior before it is referenced within the behavior, but is not referenced outside the behavior, will be eliminated by the synthesis process.

## SYNTHESIS TIP

A variable that is assigned value by an edge-sensitive behavior and is referenced outside the behavior will be synthesized as the output of a flip-flop.

## Example (6.16):

| module or4_    | _behav (y, x_in);    |          |

|----------------|----------------------|----------|

|                | word_length = 4;     |          |

| output         |                      | у;       |

| input          | [word_length - 1: 0] | x_in;    |

| reg<br>integer |                      | y;<br>k; |

| megor          |                      | •••      |

```

always @ x_in

begin: check_for_1

y = 0;

for (k = 0; k <= word_length -1; k = k+1)

if (x_in[k] == 1) begin

y = 1;

disable check_for_1;

end

end

end

endmodule</pre>

```

Synthesis result: 4-input OR gate

Note: The register variable k is eliminated by the synthesis process.

#### Example 6.25

*D\_out* is not referenced outside the scope of the behavior

A synthesis tool will eliminate *D\_out*. output of a flip-flop.

```

module empty_circuit (D_in, clk);

input D_in;

input clk;

reg D_out;

always @ (posedge clk) begin

D_out <= D_in;

end

endmodule</pre>

```

Note: If *empty\_circuit* is modified to declare *D\_out* as an output port, *D\_out* will be synthesized as the output of a flip-flop.

## Synthesis of Explicit State Machines

Features of explicit state machines:

- Explicitly declared state register

- Explicit logic or state evolution

Explicit machines can be described by two behaviors

- Edge-sensitive behavior that synchronizes the evolution of the state

- Level-sensitive behavior that describes the next state and output logic.

```

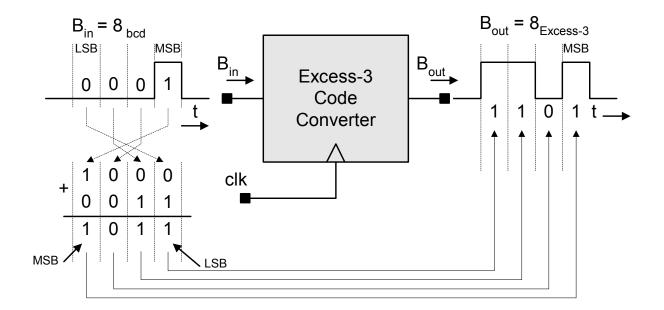

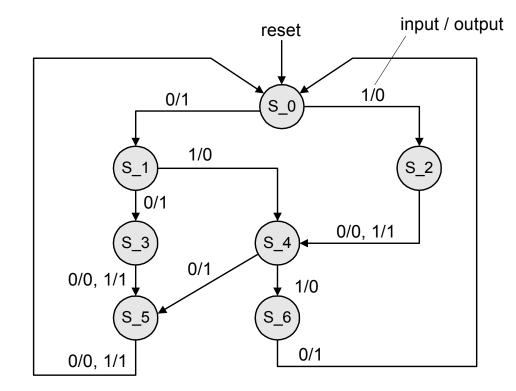

Example: BCD-to-Excess-3 Code Converter (Mealy)

```

See Example 3.2 for manual design

- A serially-transmitted BCD (8421 code) word is to be converted into an Excess-3 code

- An Excess-3 code word is obtained by adding 3 to the decimal value and taking the binary equivalent. Excess-3 code is self-complementing

| Decimal<br>Digit | 8-4-2-1<br>Code<br>(BCD) | Excess-3<br>Code |

|------------------|--------------------------|------------------|

| 0                | 0000                     | 0011             |

| 1                | 0001                     | 0100             |

| 2                | 0010                     | 0101             |

| 3                | 0011                     | 0110             |

| 4                | 0100                     | 0111             |

| 5                | 0101                     | 1000             |

| 6                | 0110                     | 1001             |

| 7                | 0111                     | 1010             |

| 8                | 1000                     | 1011             |

```

module BCD_to_Excess_3b (B_out, B_in, clk, reset_b);

output B out;

input B in, clk, reset b;

parameter S_0 = 3'b000, // State assignment

S 1 = 3'b001.

S 2 = 3'b101,

S 3 = 3'b111.

S 4 = 3'b011,

S = 3'b110,

S = 3'b010,

dont_care_state = 3'bx,

dont care out = 1'bx;

reg[2: 0] state, next_state;

B_out;

reg

always @ (posedge clk or negedge reset_b)

```

```

if (reset_b == 0) state <= S_0; else state <= next_state;

```

```

always @ (state or B_in) begin

B out = 0;

case (state)

S 0: if (B in == 0) begin next state = S 1; B out = 1; end

else if (B in == 1) begin next_state = S_2; end

S 1: if (B in == 0) begin next state = S 3; B out = 1; end

else if (B in == 1) begin next state = S 4; end

S 2: begin next state = S 4; B out = B in; end

S 3: begin next_state = S_5; B_out = B_in; end

S_4: if (B_in == 0) begin next_state = S_5; B_out = 1; end

else if (B in == 1) begin next state = S 6; end

S 5: begin next state = S 0; B out = B in; end

S_6: begin next_state = S_0; B_out = 1; end

```

```

/* Omitted for BCD_to_Excess_3b version

Included for BCD_to_Excess_3c version

default: begin next_state = dont_care_state;

B_out = dont_care_out; end

*/

endcase

end

endmodule

```

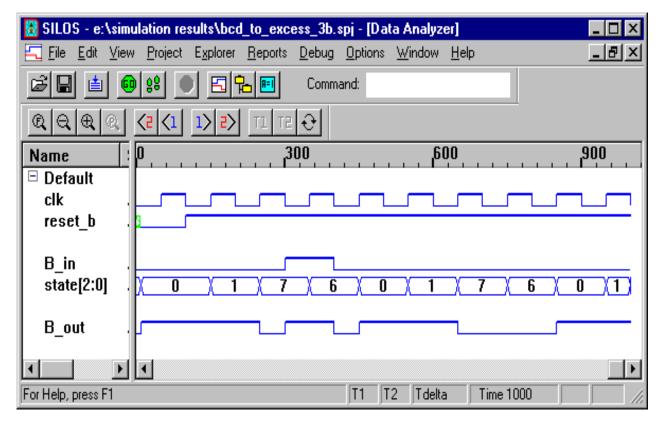

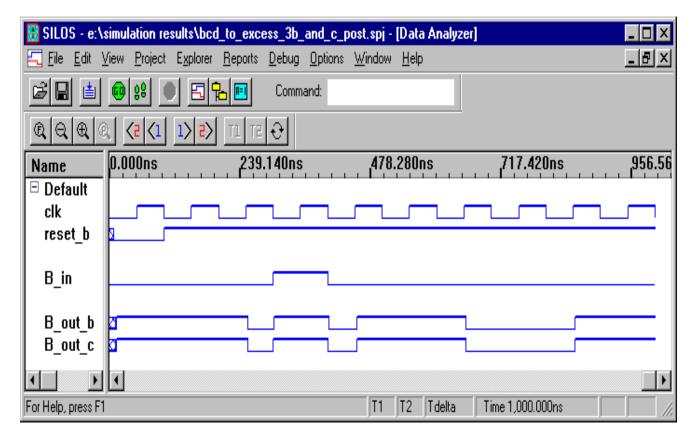

#### **Simulation r**esults for *BCD\_to\_Excess\_3b*

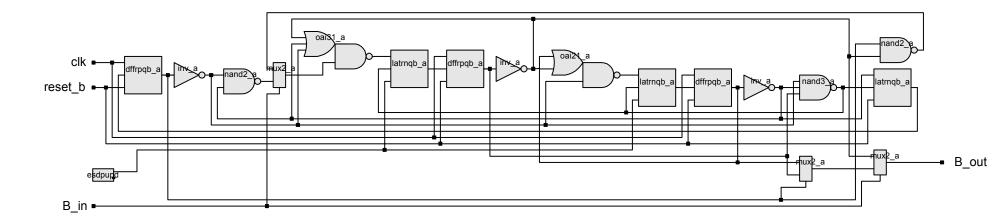

#### ASIC circuit synthesized from BCD\_to\_Excess\_3b

Note: Latches result from failure to provide default state assignments

Note: Default values for B\_out are hard-wired to 0

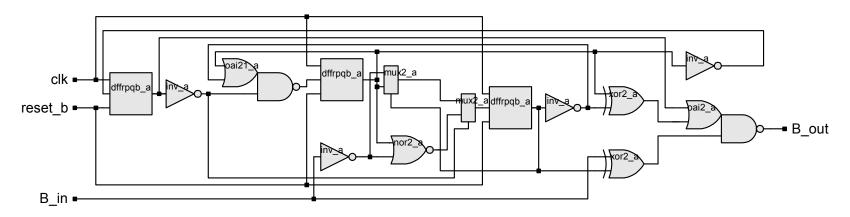

#### ASIC circuit synthesized from BCD\_to\_Excess\_3c

Note: The model includes default don't care state assignments and default don't care assignments to B\_out

#### Post-synthesis simulation results

Note: The circuits have same functionality, and simulation results match the manual design, but BCD\_to\_Excess\_3c wastes hardware

Use two cyclic behaviors to describe an explicit state machine: a level-sensitive behavior to describe the combinational logic for the next state and outputs, and an edge-sensitive behavior to synchronize the state transitions.

Use the procedural assignment operator (=) in the levelsensitive cyclic behaviors describing the combinational logic of a finite state machine.

# SYNTHESIS TIP

Use the non-blocking assignment operator (<=) in the edgesensitive cyclic behaviors describing the state transitions of a finite state machine and the register transfers of the datapath of a sequential machine.

Decode all possible states in a level-sensitive behavior describing the combinational next state and output logic of an explicit state machine.

#### Additional Rules for Synthesis

- Assign value to the entire state vector (no bit or part select allowed)

- Asynchronous control signals (e.g., set and reset) in the event control expression must be scalars

- The value that is assigned to the state register must be either a constant or a variable that evaluates to a constant after static evaluation (i.e., the state transition diagram must specify a fixed relationship)

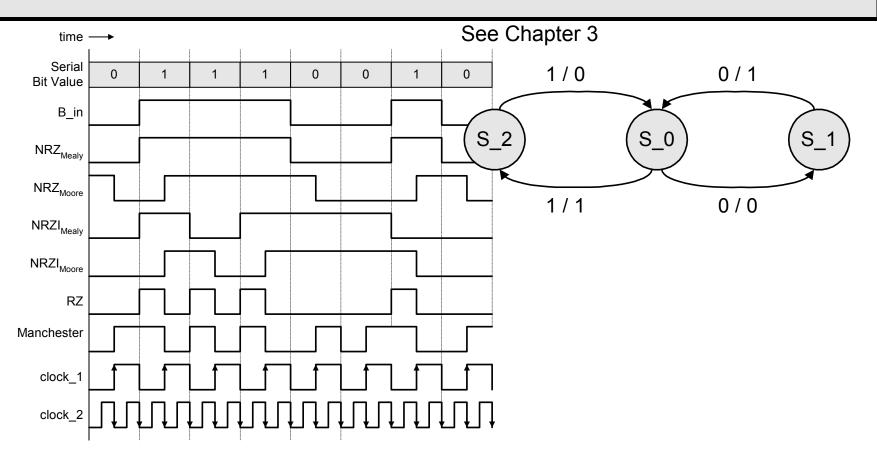

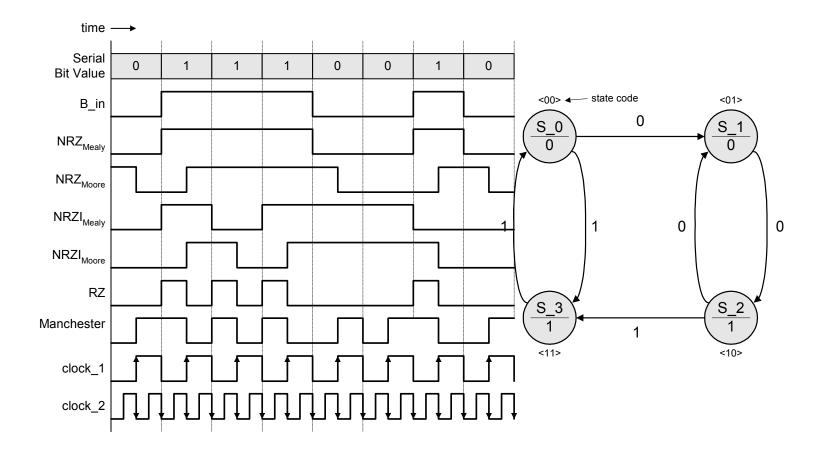

# Example: Mealy-Type NRZ-to-Manchester Line Code Converter

```

module NRZ_2_Manchester_Mealy (B_out, B_in, clock, reset_b);

```

| output<br>input<br>input<br>reg [1: 0]<br>reg<br>parameter | S_1 = 1,<br>S_2 = 2,<br>dont_care_state = 2'bx, |

|------------------------------------------------------------|-------------------------------------------------|

|                                                            | dont_care_out = 1'bx;                           |

```

always @ (negedge clock or negedge reset_b)

if (reset_b == 0) state <= S_0; else state <= next_state;</pre>

```

Note:

- *B\_in* is switching on active edges of *clock\_1* (alternate active edges of *clock\_2*)

- *B\_in* changes at the same time as the state

- General rule: avoid having the inputs change at the same time that the state changes unless it happens that the inputs are treated as don't-cares at those edges

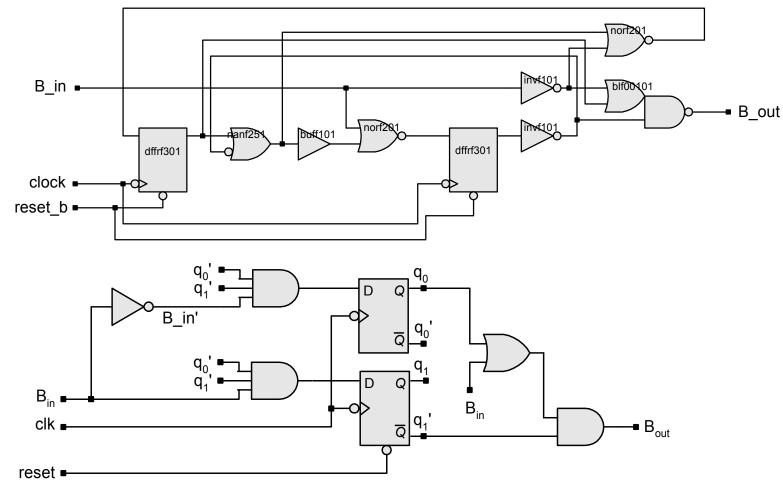

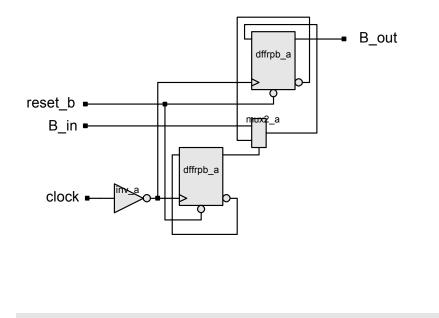

#### Synthesis Netlist

```

module NRZ 2 Manchester Mealy (B out, B in, clock, reset);

input B in, clock, reset:

output B out;

wire hext state < 1 >, hext state < 0 >, state < 1 >, state < 0 >, n80, n81, n82, n83;

buff101 U26 ( .A1(n81), .O(n80) );

norf201 U27 ( .A1(n81), .B1(n82), .O(\next state<1> ) );

norf201 U28 ( .A1(B in), .B1(n80), .O(\next state<0> ) );

blf00101 U29 ( .A1(n83), .B2(\state<1> ), .C2(n82), .O(B out) );

nanf251 U30 ( .A1(\state<1> ), .B2(n83), .O(n81) );

invf101 U31 ( .A1(B in), .O(n82) );

invf101 U32 ( .A1(\state<0> ), .O(n83) );

dfrf301 \state reg<1> (.DATA1(\next state<1>), .CLK2(clock), .RST3(

reset), .Q(\state<1>));

dfrf301 \state reg<0> (.DATA1(\next_state<0>), .CLK2(clock), .RST3(

reset), Q(state < 0 >);

endmodule

```

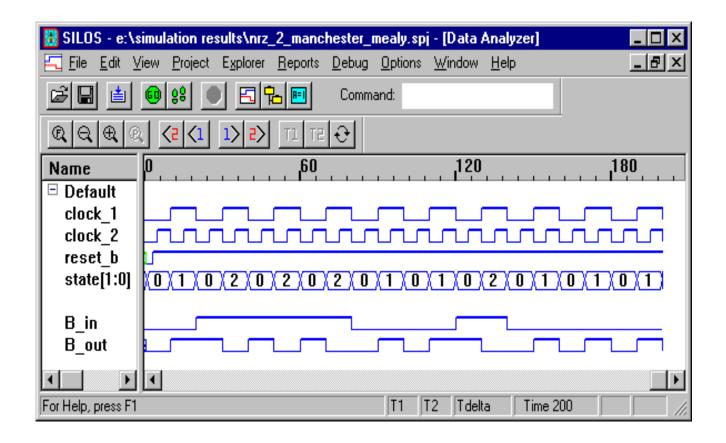

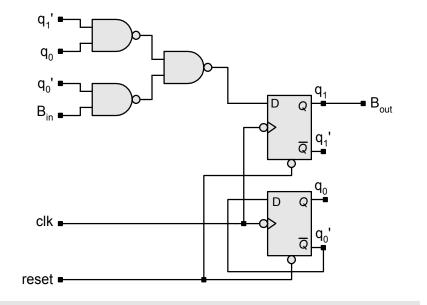

## Synthesized Circuit (Compared to Chapter 3 result)

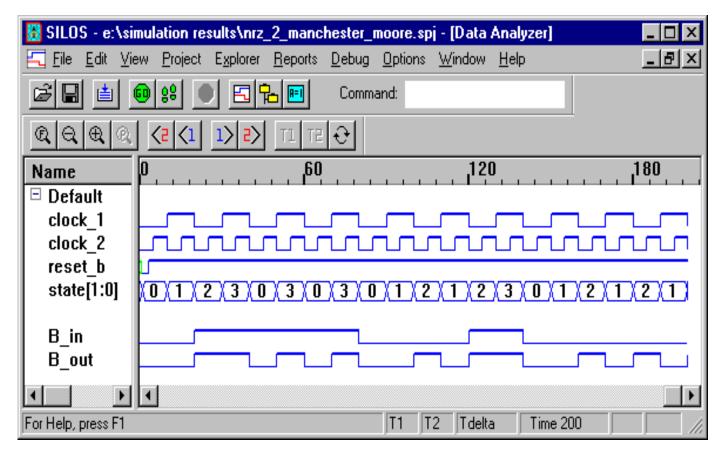

# Moore-Type NRZ-to-Manchester Line Code Converter

```

always @ (negedge clock or negedge reset_b)

if (reset_b == 0) state <= S_0; else state <= next_state;</pre>

```

#### Simulation Results:

## Synthesis Results (Compared to Chapter 3):

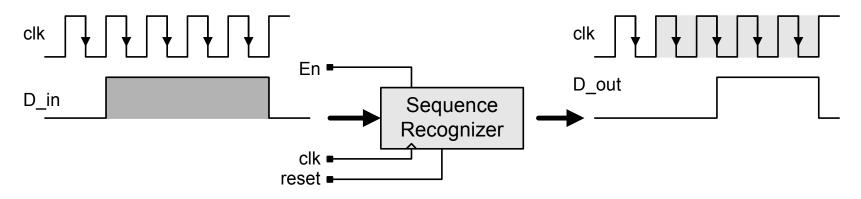

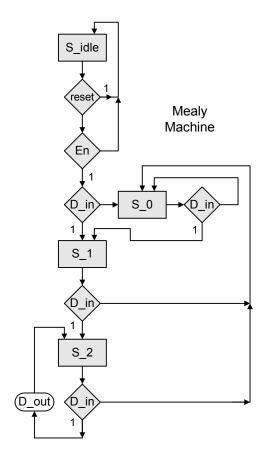

## Example: Sequence Recognizer

Detect three successive 1s

- Assert *D\_out* when a given pattern of consecutive bits has been received in its serial input stream, *D\_in*

- Apply data on the rising edge of the clock if the state transitions are to occur on the falling edge of the clock, and visa-versa.

Conventions:

- The output of a Mealy machine is valid immediately before the active edge of the clock controlling the machine

- Successive values inputs are received in successive clock cycles.

- A *non-resetting* machine continues to assert its output if the input bit pattern is overlapping

- A resetting machine asserts for one cycle after detecting the input sequence, and then de-asserts for one cycle before detecting the next sequence of bits

```

module Seq_Rec_3_1s_Mealy (D_out, D_in, En, clk, reset);

```

| output<br>input<br>input                         | D_out;<br>D_in, En;<br>clk, reset; |                      |                |

|--------------------------------------------------|------------------------------------|----------------------|----------------|

| parameter<br>parameter<br>parameter<br>parameter | S_1 =                              | 0;<br>1;<br>2;<br>3; | // Binary code |

**reg** [1: 0] state, next\_state;

always @ (negedge clk)

if (reset == 1) state <= S\_idle; else state <= next\_state;</pre>

| case (state)               | ·                                        | artially decoded<br>= 1)) next_state = S_1; <b>else</b><br>= 0)) next_state = S_0;<br>next_state = S_idle; |

|----------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------|

| S_0:                       | if (D_in == 0)<br>if (D_in == 1)<br>else | next_state = S_0; <b>else</b><br>next_state = S_1;<br>next_state = S_idle;                                 |

| S_1:                       | if (D_in == 0)<br>if (D_in == 1)<br>else | next_state = S_0; <b>else</b><br>next_state = S_2;<br>next_state = S_idle;                                 |

| S_2:                       | if (D_in == 0)<br>if (D_in == 1)<br>else | next_state = S_0; <b>else</b><br>next_state = S_2;<br>next_state = S_idle;                                 |

| default:<br>endcase<br>end |                                          | next_state = S_idle;                                                                                       |

assign D\_out = ((state == S\_2) && (D\_in == 1 )); // Mealy output

endmodule

```

module Seq_Rec_3_1s_Moore (D_out, D_in, En, clk, reset);outputD_out;inputD_in, En;inputclk, reset;

```

| parameter | S_idle = | 0; | <pre>// Binary code</pre> |

|-----------|----------|----|---------------------------|

| parameter | S_0 =    | 1; |                           |

| parameter | S_1 =    | 2; |                           |

| parameter | S_2 =    | 3; |                           |

| parameter | S_3 =    | 4; |                           |

**reg** [2: 0] state, next\_state;

```

always @ (negedge clk)

```

if (reset == 1) state <= S\_idle; else state <= next\_state;

always @ (state or D in) begin case (state) if ((En == 1) && (D in == 1)) next state = S 1; else S idle: **if** ((En == 1) && (D\_in == 0)) next\_state = S\_0; next\_state = S\_idle; else S 0: **if** (D in == 0) next state = S 0; else next\_state = S\_1; **if** (D\_in == 1) next state = S idle; else S 1: **if** (D in == 0) next state = S 0; else if (D\_in == 1) next state =  $S_{2}$ ; else next state = S idle; S 2, S 3: **if** (D in == 0) next state = S 0; else if (D\_in == 1) next state =  $S_{3}$ ; else next state = S idle: default: next state = S idle; endcase end **assign** D out = (state == S 3); // Moore output endmodule

module t\_Seq\_Rec\_3\_1s ();

reg D\_in\_NRZ, D\_in\_RZ, En, clk, reset;

```

wire Mealy_NRZ;

wire Mealy_RZ;

wire Moore_NRZ;

wire Moore_RZ;

```

```

Seq_Rec_3_1s_Mealy M0 (Mealy_NRZ, D_in_NRZ, En, clk, reset);

Seq_Rec_3_1s_Mealy M1 (Mealy_RZ, D_in_RZ, En, clk, reset);

Seq_Rec_3_1s_Moore M2 (Moore_NRZ, D_in_NRZ, En, clk, reset);

Seq_Rec_3_1s_Moore M3 (Moore_RZ, D_in_RZ, En, clk, reset);

```

initial #275 \$finish;

```

initial begin #5 reset = 1; #1 reset = 0; end

initial begin

clk = 0; forever #10 clk = ~clk;

end

initial begin

#5 En = 1;

#50 En = 0;

end

```

```

initial fork

begin #10 D_in_NRZ = 0; #25 D_in_NRZ = 1; #80 D_in_NRZ = 0; end

begin #135 D_in_NRZ = 1; #40 D_in_NRZ = 0; end

begin #195 D_in_NRZ = 1'bx; #60 D_in_NRZ = 0; end

join

```

#### initial fork

```

#10 D_in_RZ = 0;

#35 D_in_RZ = 1; #45 D_in_RZ = 0;

#55 D_in_RZ = 1; #65 D_in_RZ = 0;

#75 D_in_RZ = 1; #85 D_in_RZ = 0;

#95 D_in_RZ = 1; #105 D_in_RZ = 0;

#135 D_in_RZ = 1; #145 D_in_RZ = 0; #155 D_in_RZ = 1; #165 D_in_RZ = 0;

#195 D_in_RZ = 1'bx; #250 D_in_RZ = 0;

join

endmodule

```

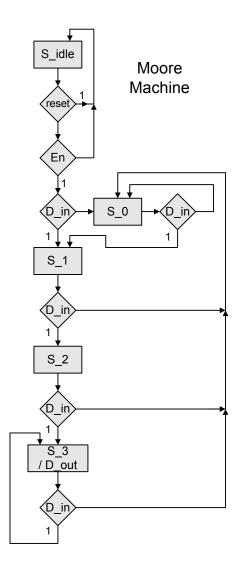

Note:

The Mealy machine is non-resetting

The Moore machine does not anticipate *D\_in*

The Mealy machine anticipates *D\_in* and asserts *D\_out* before the third clock

The Mealy machine asserts D\_out in the state reached after the third active edge of the clock

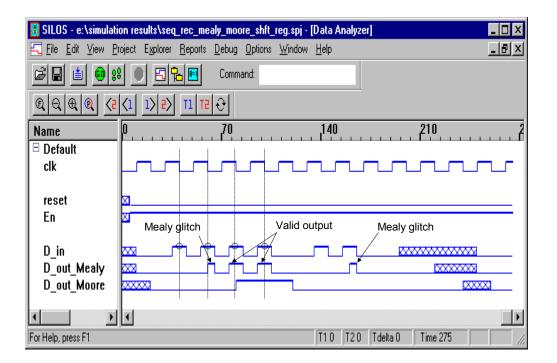

### Simulation results

- Testbench includes RZ and NRZ input formats

- The Mealy machine has an invalid assertion of its output when the input has an RZ format, an apparent glitch

- Mealy glitch occurs immediately after the second clock and persists until D\_in is de-asserted

- The valid Mealy output is 0, which is the value of *Mealy\_RZ* immediately before the second clock

- The value of *Mealy\_RZ* immediately before the third clock is 1(valid output)

- Notice behavior if B\_in = x

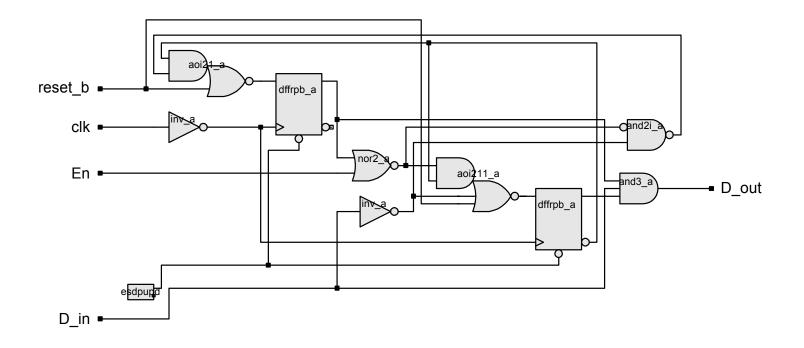

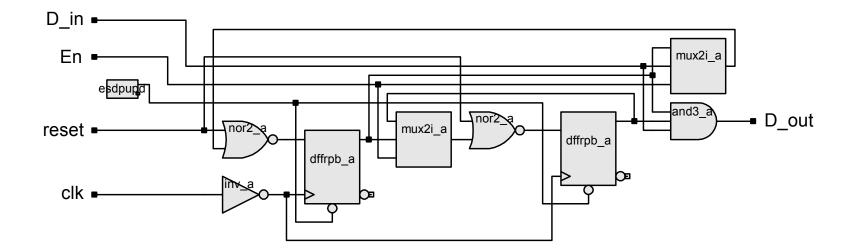

## Synthesis Result: Mealy Machine

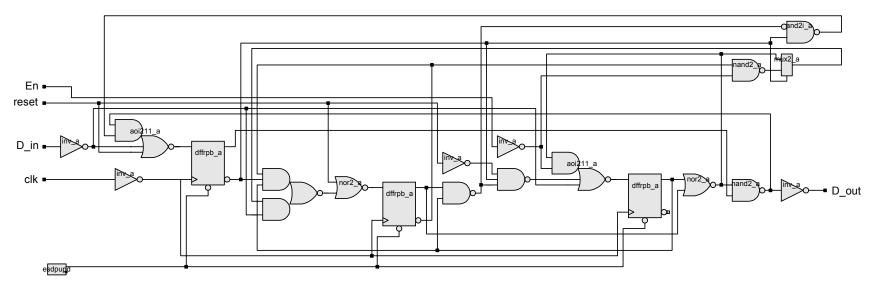

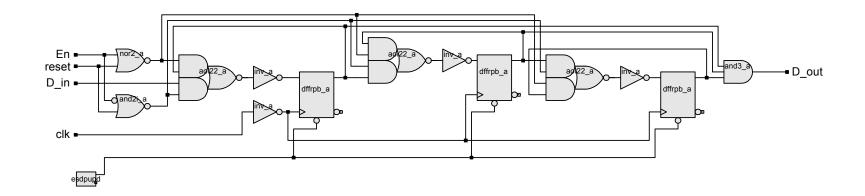

## Synthesis Result: Moore Machine

### Note: Circuit includes logic to default to S\_idle if En is de-asserted

(b)

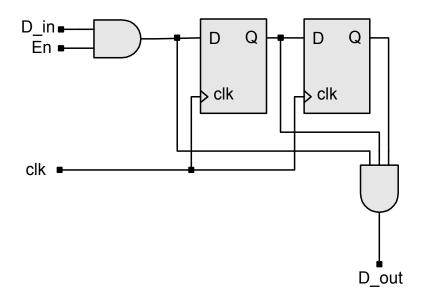

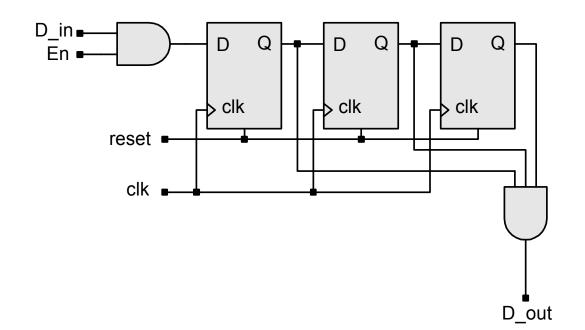

Alternative approach: Shift input bits through a register and detect contents

Note: The Mealy machine below differs from the previous implementation by gating the datapath with *En*

Moore Machine:

Note: an explicit state machine implementation of a sequence recognizer is not necessarily the most efficient implementation

```

module Seq_Rec_3_1s_Mealy_Shft_Reg (D_out, D_in, En, clk, reset);

```

```

output

D_out;

input

D_in, En;

input

clk, reset;

parameter

Empty = 2'b00;

reg

[1: 0]

Data;

```

```

always @ (negedge clk)

if (reset == 1) Data <= Empty; else if (En == 1) Data <= {D_in, Data[1]};</pre>

```

assign D\_out = ((Data == 2'b11) && (D\_in == 1 )); // Mealy output

endmodule

```

module Seq_Rec_3_1s_Moore_Shft_Reg (D_out, D_in, En, clk, reset);

output D_out;

input D_in, En;

input clk, reset;

parameter Empty = 2'b00;

reg [2: 0] Data;

```

```

always @ (negedge clk)

if (reset == 1) Data <= Empty; else if (En == 1) Data <= {D_in, Data[2:1]};</pre>

```

```

assign D_out = (Data == 3'b111); // Moore output

endmodule

```

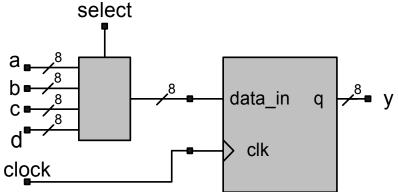

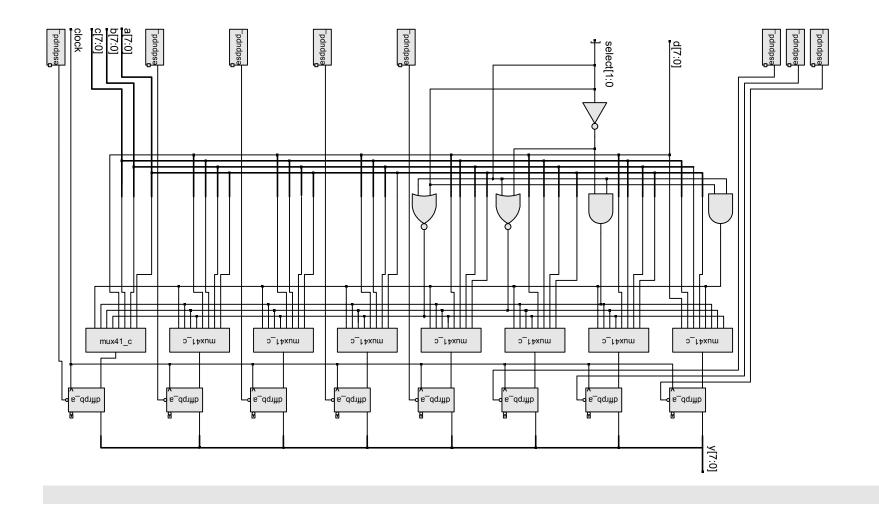

# **Registered Logic**

- Variables whose values are assigned synchronously with a clock signal are said to be *registered*.

- Registered signals are updated at the active edges of the clock and are stable otherwise

**Example: Registered Logic**

```

module mux_reg (y, a, b, c, d, select, clock);

output [7: 0] y;

input [7: 0] a, b, c, d;

input [1: 0] select;

input clock;

reg [7: 0] y;

always @ (posedge clock)

case (select)

0: y <= a; // non-blocking

1: y <= b;

2: y <= c;

3: y <= d;

default y <= 8'bx;</pre>

```

endcase

endmodule

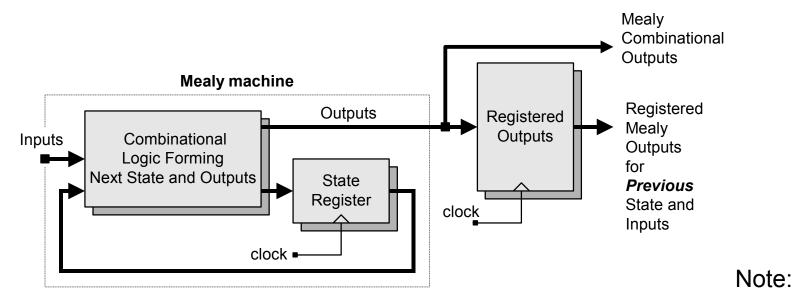

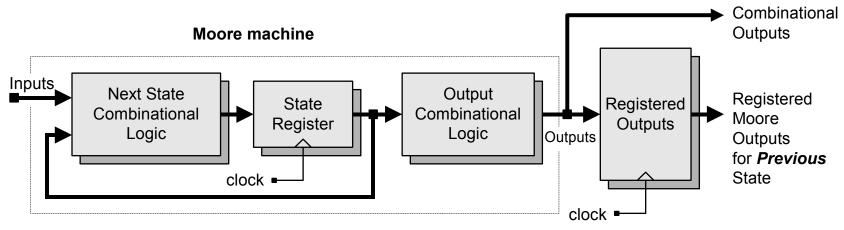

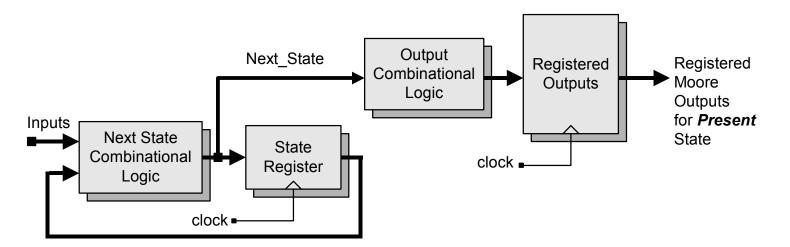

## Sequential Machines with Registered Outputs

- Outputs can be registered to prevent glitches from affecting the logic driven by the outputs of the machine.

- Several options

- The output of the storage register lags the combinational values by one clock cycle

- The output of the register corresponds to the state of the machine in the previous cycle

- The output of the storage register lags the combinational values by one clock cycle

- The output of the register corresponds to the state of the machine in the previous cycle

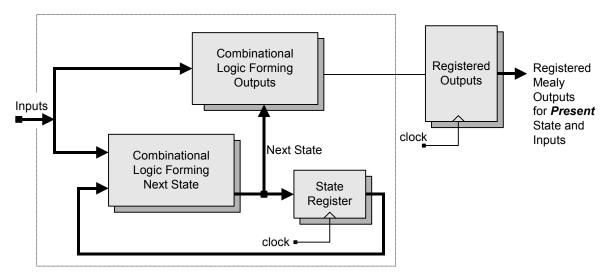

- The registered outputs are formed in the same cycle as the state

- The Mealy outputs are formed from the next state and the inputs at the active edge of the clock

- The value stored in the output register corresponds to the state reached at the clock transition and the inputs that caused the transition

•

Note: The value stored in the output register will correspond to the state that is stored in the state register

Example: Sequence Recognizer with Registered Outputs

Include the following code in Seq\_Rec\_3\_1s\_Mealy:<sup>1</sup>

```

reg D_out_reg;

always @ (negedge clk)

if (reset == 1) D_out_reg <= 0;

else D_out_reg <= ((state == S_2) && (next_state == S_2) && (D_in

== 1 ));

```

Notice that the clause (*state* ==  $S_2$ ) is included in the logic to prevent a premature assertion while the state of the machine is  $S_1$  (see the ASM chart in Figure 6.38b).

<sup>&</sup>lt;sup>1</sup> The port declarations of each machine must be modified to include the registered output.

Include the following code in *Seq\_Rec\_3\_1s\_Moore*:

```

reg D_out_reg;

always @ (negedge clk)

if (reset == 1) D_out_reg <= 0; else D_out_reg <= (next_state ==

S_3);

```

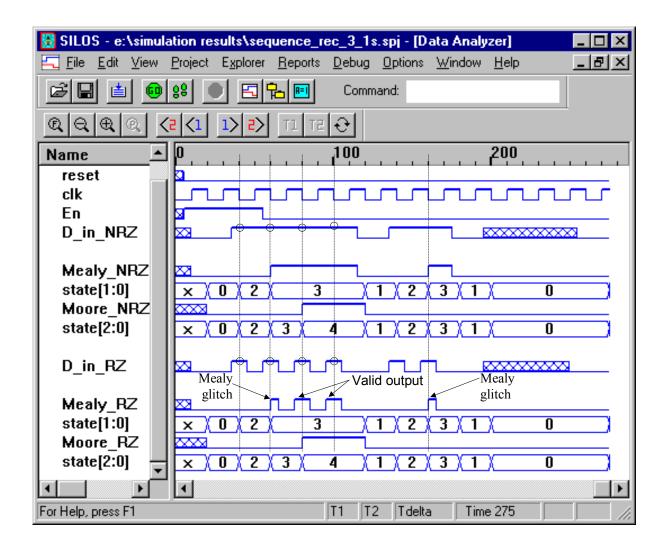

### **Simulation Results:**

| 🔢 SILOS - e:\simulation result | s\sequence_rec_3_1s_registered.spj - [Data Analyzer]                            |

|--------------------------------|---------------------------------------------------------------------------------|

| Edit View Project Ex           | plorer <u>R</u> eports <u>D</u> ebug <u>Options</u> <u>W</u> indow <u>H</u> elp |

|                                | E Command:                                                                      |

|                                |                                                                                 |

|                                |                                                                                 |

| Name                           | 0                                                                               |

| 🖻 Default                      |                                                                                 |

| reset                          | <b>a</b>                                                                        |

| clk                            |                                                                                 |

| En                             |                                                                                 |

| D in NRZ                       |                                                                                 |

| state[1:0]                     | $\mathbf{x}$ $(0)$ $(2)$ $(3)$ $(1)$ $(2)$ $(3)$ $(1)$ $(0)$                    |

| Mealy_NRZ                      |                                                                                 |

| Mealy_NRZ_registered           |                                                                                 |

| state[2:0]                     | x 0 2 3 4 1 2 3 1 0                                                             |

| Moore_NRZ                      |                                                                                 |

| Moore_NRZ_registered           |                                                                                 |

| D_in_RZ                        |                                                                                 |

| state[1:0]                     | × (0 (2 ) 3 (1 (2 ) 3 (1 ) 0                                                    |

| Mealy_RZ                       |                                                                                 |

| Mealy_RZ_registered            |                                                                                 |

| state[2:0]                     | x 0 2 3 4 1 2 3 1 0                                                             |

| Moore_RZ                       |                                                                                 |

| Moore_RZ_registered            |                                                                                 |

| <u>۱</u>                       |                                                                                 |

| For Help, press F1             | T1 T2 Tdelta Time 275 ///                                                       |

- Registered and unregistered outputs for NRZ and RZ formatted serial inputs

- The unregistered output of the Mealy machine changes with the input

- The registered output does not change with the input to the machine

- The value of the registered Mealy output corresponds to the value implied by the input and next state at the active (falling) edge of the clock

- The unregistered output anticipates the clock

- The output of the registered machine does not

- The waveforms of the registered and unregistered Moore outputs are identical

- The output of the unregistered machine is formed by combinational logic

- The output of the registered machine the output is the output of a register

# State Encoding

| #  | Binary | One-Hot                                 | Gray | Johnson  |

|----|--------|-----------------------------------------|------|----------|

| 0  | 0000   | 000000000000000000000000000000000000000 | 0000 | 00000000 |

| 1  | 0001   | 000000000000010                         | 0001 | 0000001  |

| 2  | 0010   | 000000000000100                         | 0011 | 00000011 |

| 3  | 0011   | 000000000001000                         | 0010 | 00000111 |

| 4  | 0100   | 000000000010000                         | 0110 | 00001111 |

| 5  | 0101   | 000000000100000                         | 0111 | 00011111 |

| 6  | 0110   | 00000000100000                          | 0101 | 00111111 |

| 7  | 0111   | 00000001000000                          | 0100 | 01111111 |

| 8  | 1000   | 00000010000000                          | 1100 | 11111111 |

| 9  | 1001   | 00000100000000                          | 1101 | 11111110 |

| 10 | 1010   | 000001000000000                         | 1111 | 11111100 |

| 11 | 1011   | 0000100000000000                        | 1110 | 11111000 |

| 12 | 1100   | 000100000000000                         | 1010 | 11110000 |

| 13 | 1101   | 001000000000000                         | 1011 | 11100000 |

| 14 | 1110   | 010000000000000                         | 1001 | 11000000 |

| 15 | 1111   | 100000000000000                         | 1000 | 10000000 |

- A binary coded decimal format (BCD uses the minimal number of flip-flops, but does not necessarily lead to an optimal realization of the combinational logic used to decode the next state and output of the machine.

- If a machine has more than 16 states, a binary code will result in a relatively large amount of next-state logic; the machine's speed will also be slower than alternative encoding.

- A Gray code uses the same number of bits as a binary code, but has the feature that two adjacent codes differ by only one bit, which can reduce the electrical noise in a circuit.

- A Johnson code has the same property, but uses more bits.

- A code that changes by only one bit between adjacent codes will reduce the simultaneous switching of adjacent physical signal lines in a circuit, thereby minimizing the possibility of electrical crosstalk.

- These codes also minimize transitions through intermediate states.

## **One-Hot Codes**

- One flip-flop for each state

- Reduces the decoding logic for next state and output

- Complexity does not increase as states are added to the machine

- Tradeoff: speed is not compromised by the time required to decode the state

- Cost: area of the additional flip flops and signal routing

- A one-hot encoding with an *if* statement that tests individual bits might provide simpler decoding logic than decoding with a case statement

- One-hot encoding usually does not correspond to the optimal state assignment

- Use one-hots in Xilinx to reduce the use of CLBs

- Note: in large machines, one-hot encoding will have several unused states, in addition to requiring more registers than alternative encoding

- Gray encoding is recommended for machines having more than 32 states because it requires fewer flip-flops than one-hot encoding, and is more reliable than binary encoding because fewer bits change simultaneously.

- Caution: if a state assignment does not exhaust the possibilities of a code, then additional logic will be required to detect and recover from transitions into unused states.